Quick start Guide to Using

Envisia Ambit Synthesis Tool from Cadence

01. Introduction

Logic Synthesis with the Cadence Ambit synthesizer takes a circuit description given in behavioral (it is not necessary to synthesize structural descriptions) hardware description language (VHDL or Verilog) and produces a netlist ( structural description) of an implementation of the circuit out of logic gates contained in a library. The cadence verliog simulator uses the netlist as input so that the function and timing of the circuit can be verified.

02. Invoking Ambit

After invoking the Cadence environment by typing "cds" in the console window, cd to ece484/verilog.src. At the command prompt in the console, type in "ambit". This will invoke the Envisia Ambit Synthesis Tool and will be as shown in Fig:1

Figure - 1

03. Setting the Environment in Ambit.

In the ambit window, at the command prompt (pks_shell[] >), we define a WORK library as shown below. Ambit requires a default library to generate intermediate synthesis files.

pks_shell[1]> set library_root /home/cdsadmin/vendors/VTVT/SPR/

This will load the library_root with the path specified.

04.Synthesis with Ambit

The design file is compiled by the following command.

pks_shell[2]> read_verilog /home/<username>/cds/EE484/verilog.src/cnt8bit.v

Build a Generic Netlist by typing the following command at the prompt in the Ambit Window

pks_shell[3]> do_build_generic -all

The do_build_generic -all command generated Control Data Flow Graphs (CDFG), performs high level optimization, resource allocation and also generates a netlist for the module defined. The netlist created is not technology specific but is based on the ATL (Ambit technology library) cells.

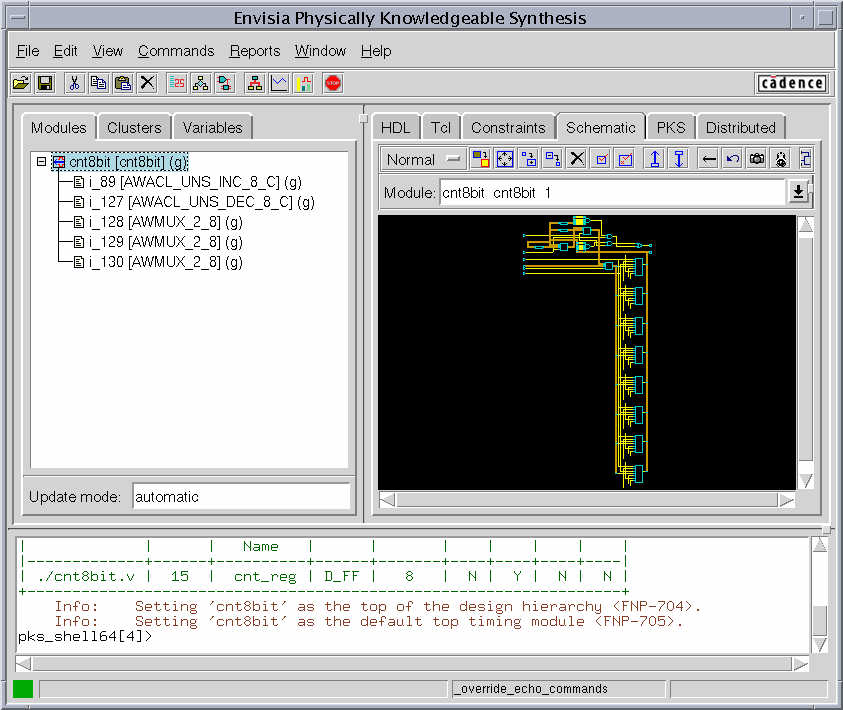

From the menu click on schematic and then double click on the cnt8bit in the left window (It has been highlighted in red in figure 2). You should now see a schematic with the individual blocks of the counter 8 bit. You may have to click on the "cnt8bit" icon. See in Fig. 2. Try zoom-in and zoom-out to check out the details of the design.. Double clicking on a hierarchical module leads to the lower level detailed schematic for that block (You can try this on the counter module).

Fig : 2

The Structural Verilog Code of cnt8bit before optimization can be written to a file by issuing the following command:

pks_shell[4]> write_verilog /home/<username>/cds/ece484/verilog.src/cnt8bitbeforeopt.v

This command will write the gate level description or the structural description in the file "cnt8bitbeforeopt.v".

04. Setting the Constraints:

By default Ambit tries to synthesize for minimum area. Other constraints for the design must be specified by the user.

1. The first step is to specify the module for which you want to set the constraints.

pks_shell[5]> set_top_timing_module cnt8bit

2. For all sequential logic the constraints are specified with reference to a clock. Therefore all clock must be defined.

pks_shell[6]> set_clock clock -period <period in ns> -waveform <{duty cycle}> (General - Case)

pks_shell[6]>set_clock clk -period 10.0 -waveform {0.0 5.0}

The above command defines an ideal clock, clock, with a period of 10ns and a duty cycle of 5ns. The duty cycle is specified with a rising edge at 0.0ps and a falling edge at 5.0ps. It is important to note that set_clock defines an ideal clock and does not refer to any port of the actual design.

3. The next step is to define the relationship of the actual clock with that of the ideal clock.

pks_shell[7]> set_clock_arrival_time -rise 0.1 -fall 5.1 -clk clk

These are all the constraints that we will set for this exercise. However, there are a variety of other constraints that are possible to set.

05.Technology Specific Synthesis

Thus far the logic synthesis procedure has been technology independent. The atl and the ambit_xatl libraries are generic libraries that are automatically loaded when pks_shell is invoked. The do_build_generic command generates a netlist in which the cells from atl and ambit_xatl are used. In this step we map our design to a specific technology and then perform optimization.

1. The first step is to specify a target library. We use the TSMC quarter Micron Deep Process. In order to do this issue the following commands in the command window of the ambit window.

pks_shell[8]> read_alf ${library_root}/ALF/cells.alf

pks_shell[9]> read_lef ${library_root}/LEF/cells.lef

2. The next step is to optimize the design in the target technology. Type the following command in the ambit command window

pks_shell[10]> do_optimize -pks

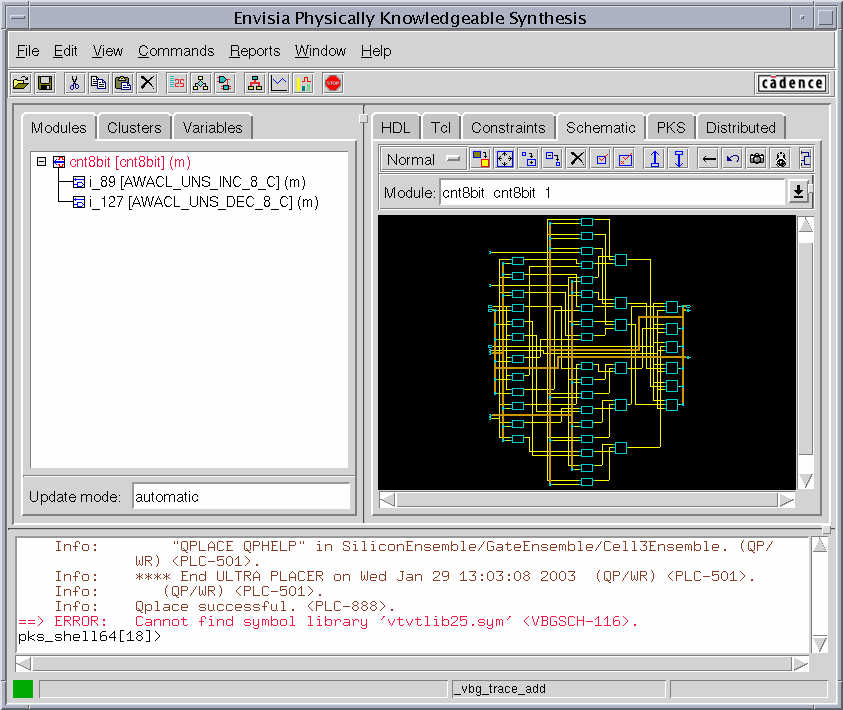

Fig. 3 shows the design synthesized in the target library. Again double clicking on any module will show the detailed design of the individual modules. A summary of area and timing is also reported.

Fig:3

The do_optimize command is the basic minimum command required to synthesize a design in a technology specific library. Ambit has considerable number of other commands and options to synthesize more aggressively.

Step6: Report Generation

Detailed area and timing reports can also be generated and directed to a file. The report area command is used for this. The command below is used to direct the report to a file called area.rpt.

pks_shell[11]> report_area -hierarchical -cell /home/<username>/cds/ece484/verilog.src/cnt8bitarea.rpt

Similarly a detailed timing report is generated in the file timing.rpt by the following command

pks_shell[12]> report_timing /home/<username>/cds/ece484/verilog.src/cnt8bittiming.rpt

Step7: Structural Verilog Code of cnt8bit after optimization.

pks_shell[13]> write_verilog /home/<username>/cds/ece484/verilog.src/cnt8bitafteropt.v

This command will write the gate level description or the structural description in the file "cnt8bitafteropt.v".