Step 3 : Layout Versus Schematic

In this step we are going to compare the schematic and the extracted layout to

see if they are identical.

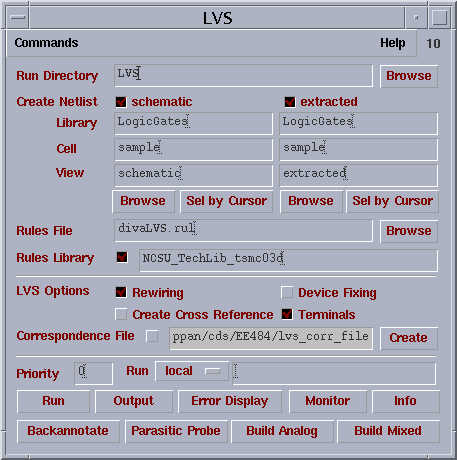

1. From the Verify menu select the option LVS.

If you had previously run a LVS check, this would pop-up a small warning box. Make sure that the option Form Contents is selected in this box.

The top half of the LVS options window is split into two parts. The part on the left corresponds to the schematic cell view and the right part corresponds to the extracted cell view that are to be compared. Make sure that the entries in these boxes represent the values for your circuit.

Although there are a number of options for LVS, the default options will be enough for basic operations, select Run to start the comparison. (Note: The Library name in the figure shows as LogiGates but we would use our library “ece484Lib”)

In the left hand side of the Create netlist box and under the schematic, click on browse, select the library name first, the cell name next and the view which will be the schematic. Follow the same steps in the right hand side and this time, the view will be extracted. Select Run to start the comparison

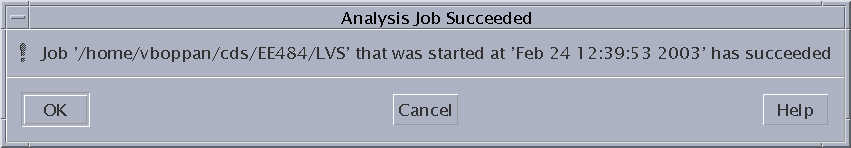

The comparison algorithm will run in the background, the result of the LVS run will be displayed in a message box. Be patient, even for a very small design the LVS run can take some time (minutes).

The succeeded message in the above message box, indicates that the LVS program has finished comparing the netlists, NOT THAT THE CIRCUITS MATCH. It might be the case that the LVS was successful in comparing the netlists and came up with the result that both circuits were different.

To see the actual result of an LVS run you have to examine the output of the LVS run. The Output option is right next to the Run command

Note: The output of the LVS what you get will not be equal to the output in the tutorial.

You can take a look at the complete LVS result in the "output". It states that the netlists did indeed match. If you discover that there is a mismatch, you must go back to the layout view and correct the error(s).

Most of the other options on the LVS form, are for finding mismatches between two netlists and to generate netlists that include only parasitic effects relevant to one part of the circuit.